The Cisco ASR-9922-AC is a robust 20-Slot AC Chassis designed for the Cisco ASR 9922 Router, equipped with Power Entry Modules (PEMs), fans, Route Processors (RPs), and Switch Fabric Cards (SFCs). It leverages the next-generation Cisco ASR 9900 Route Processor 2 (ASR 9900 RP2) as the system processor, optimized for high-density 100 Gigabit Ethernet line cards in demanding wireline, Data-Center-Interconnect (DCI), and Radio Access Network (RAN) aggregation applications.

The ASR 9900 RP2 architecture supports programmable deployment models and convergence of Layer 2 and Layer 3 services. Powered by Cisco IOS XR Software, it offers true software process modularity with each process running in separate protected memory, including routing protocols and multiple instances of control, data, and management planes. Distributed route processing ensures high scalability, performance, and fast convergence for video, cloud, and mobile services.

Key Features and Benefits

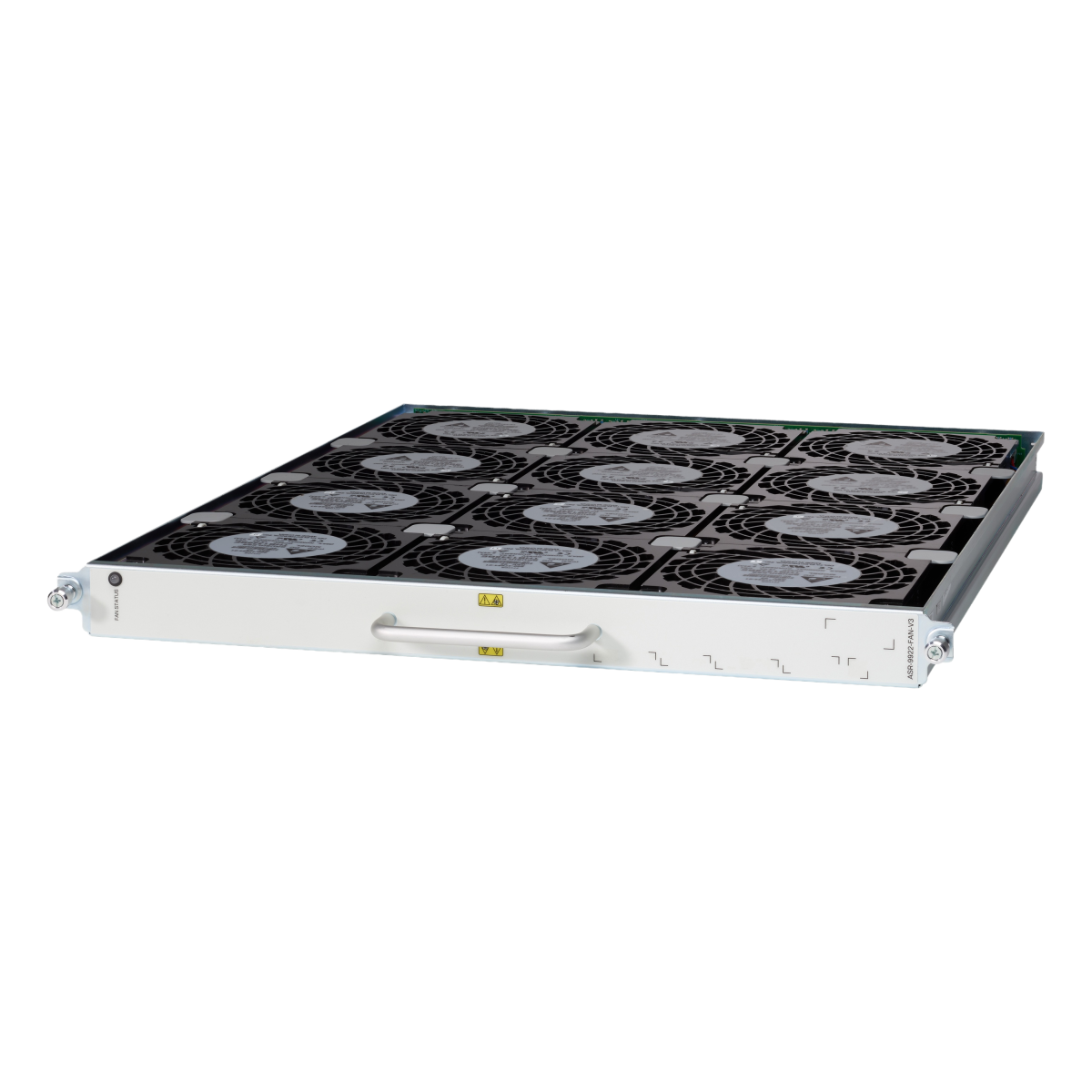

- Highly scalable fabric: Designed to support high 1-, 10-, and 100-Gbps port densities. Provides built-in scalability for investment protection.

- Control of up to seven switch fabric cards: Offers traffic load balancing simultaneously across up to seven fabrics.

- Distributed-forwarding-plane architecture: Allows line cards to support independent forwarding for enhanced performance and scale.

- Memoryless switch fabric: Provides transparent nonblocking, low-latency packet forwarding.

- Virtual output queuing and arbitration: Offers service intelligence with prioritization of traffic (unicast and multicast). Provides efficient congestion-management mechanism and avoids problems related to head-of-line blocking.

- Centralized arbiter: Uses an efficient credit mechanism to help ensure transparent switchover with zero packet loss.

- IEEE 1588 support: Delivers timing services over the packet network efficiently and reliably.

- Two independent clock source connections: BITS and Synchronization Supply Unit (SSU) DTI: Offers redundant, centralized network synchronization support.

- Two 32-GB Solid-State Drives (SSDs): Allows storing of core dumps and helps reduce the system Mean Time To Repair (MTTR).

- Embedded Universal Series Bus (eUSB) memory port: Provides access to onboard Universal Serial Bus (USB) flash-memory devices for software image storing and upgrades.

- Front-panel external USB 2.0 port: Provides access to USB flash-memory devices for quick software image loading and recovery.

- Front-panel LEDs: Provides visual indication of route-processor status (active or standby), power management, and activity on SSD.

- Management ports: Provides easy access to system console.

- Processor: Has 8 cores, 1.9 GHz.

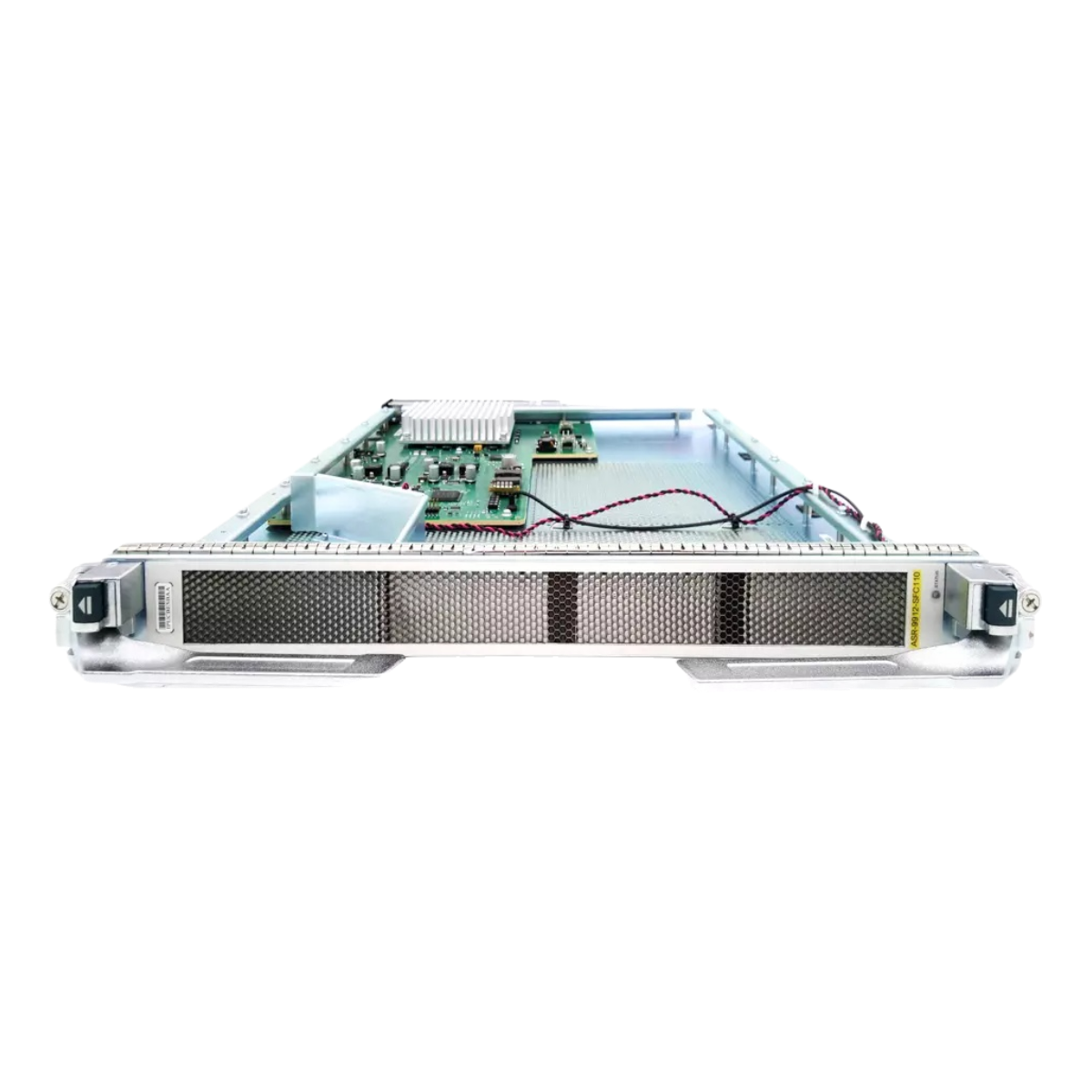

Switch Fabric Capabilities

Distributed switch fabric architecture with multistage low-latency nonblocking design. Service intelligence and traffic prioritization. Control of up to seven Cisco ASR 9900 Switch Fabric Cards for scalability and high availability on Cisco ASR 9922 chassis.

Software Features

Cisco IOS XR Software powers the platform with self-healing, distributed operation for always-on service. Supports Software-Maintenance-Updates (SMUs) for bug fixes and small features without service interruption, and Field-Programmable Device (FPD) upgrades for FPGAs, ROMmon, etc., while systems run. Key applications include Ethernet Services, L2VPN, L3VPN, IPv4/IPv6, IPTV, CDNs, mobile backhaul, IPoDWDM, SyncE, EOAM, MPLS OAM, ACLs, H-QoS, MPLS TE-FRR, MC-LAG, IRB, NSF/NSR, P2MP-TE, Lawful Intercept, Smart Call Home, MGSCP. Multiservice Edge (MSE) and Ethernet MSE (E-MSE) for business VPNs with SLA enforcement, scaling VRFs, routes, BFD, BGP NSR. Service-Edge optimized RP for high multi-dimensional scale.

Superior Network Timing

Centralized Building Integrated Timing Supply (BITS), Precision Time Protocol (PTP) IEEE 1588-2008 via dedicated 10-Mbps/100-Mbps Ethernet port, Bidirectional Time of Day (ToD) with 10-MHz and 1-pps interface. Standards-compliant PTPv2, GPS, DTI, BITS on RP, SyncE on line cards. Centralized clocking distribution to line cards.

Route Processor Models

Service-edge-optimized (higher memory for large-scale services) and packet-transport-optimized models. Both support service-optimized and transport-optimized line cards, mixable on same chassis. Common sparing with Cisco ASR 9912 chassis. Introduced on IOS XR Release 5.3.0.

High Availability and Redundancy

No single point of failure. Route-processor redundancy (identical types required). Software redundancy. Transparent switchover with zero packet loss.